№ 2(19)

## ПРОЕКТИРОВАНИЕ И ДИАГНОСТИКА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

УДК 004.312

A.Yu. Matrosova, A.V. Melnikov, R.V. Mukhamedov, S.A. Ostanin, V. Singh

## SELECTION OF THE FLIP-FLOPS FOR PARTIAL ENHANCED SCAN TECHNIQUES<sup>1</sup>

Structural scan based delay testing is used to detect delay faults. Because of the architectural limitations not each test pair  $v_1$ ,  $v_2$  can be applied by scan delay testing. That declines test coverage. Partial enhanced scan approach based on selection of flip-flops was suggested to permit using arbitrary test pairs  $v_1$ ,  $v_2$ . The problem of selection of flip-flops may be solved with applying estimations of controllability and observability of the state variables corresponding to the flip-flops. Calculation of controllability and observability estimations is based on 2-length combinational equivalent analyses and PDF testing.

**Keywords:** *Path delay fault (PDF); robust PDF; equivalent normal form (ENF).*

#### Introduction

Delay testing has become very important problem in nanometer technologies. Structural scan based delay testing is used for detecting the circuit delays. Because of the architectural limitations not each pair  $v_1$ ,  $v_2$  can be applied by a scan delay test. Enhanced scan techniques were developed to remove the restrictions on vector pairs. Unfortunately these techniques have rarely been used in practice because of the near doubling of the flip-flop area. Most promising are partial enhanced scan approaches that are based on selection of the proper flip-flops for including them in enhanced scan chains [1]. In the paper [2] it is suggested to include in scan chains flip-flops with low estimations of the 0 values of the corresponding state variables (low controllability) but facilities of propagation of changing signal values from the input to the output (observability) are not considered. In the paper [3] were suggested deriving estimations of both controllability and observability. We suggest to appreciate flip-flop controllability as sum of 01 transition probability and 10 transition probability for the corresponding state variable. The flip-flop observability is appreciated as a probability of robust PDF manifestation for the paths of the same state variable. The algorithms of controllability and observability calculation are developed.

In Section 1 the problem of calculation 01(10) transition probability for the state variable is discussed. In Section 2 the method of calculation of robust PDF manifestation probability for the paths corresponding to a state variable is suggested.

\_

<sup>&</sup>lt;sup>1</sup> Работа выполнена при финансовой поддержке Российского фонда фундаментальных исследований (грант № 11-08-92694-ИНД).

#### 1. Calculation of a probability of 01(10) transitions of state variables

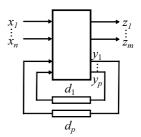

Let we have a synchronous circuit (Fig. 1) in which  $x_1,...,x_n$  are input variables,  $y_1,...,y_p$  are state variables,  $z_1,...,z_m$  are output variables, and  $d_1,...,d_p$  are flip flops.

Random input sequence of a sequential circuit is described with the probability distribution  $\rho(x_1),...,\rho(x_n)$ . Here  $\rho(x_i)$ , i=1...n, is the probability of 1 value of input variable  $x_i$ . Let assume that the probability distribution  $\rho(y_1),...,\rho(y_p)$  of state variables is also known. Here  $\rho(x_i)$ , i=1...n, is the probability of 1 value of input variable  $x_i$ .

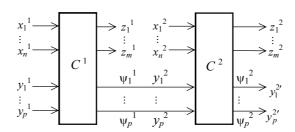

We want to calculate the probability 01(10) transition for a state variable  $y_i$ . For that consider the 2-length combinational equivalent of Fig. 2.

Having the structural description of a combinational

Fig. 1. Synchronous circuit

equivalent copy we may represent the copy functions corresponding to the combinational circuit  $C^2$  by the shared BDD which roots correspond to the state variables  $y_1^{2'}, ..., y_p^{2'}$ . These functions depend on the input variables

$x_1^2,...,x_n^2$  and the state variables  $y_1^2,...,y_p^2$  (Fig. 2). Select root correlating with the variable  $y_i^{2'}$ . All paths connecting this root with the 1-terminal node of the shared BDD represent the corresponding function  $\psi_i^2$  ( $x_1^2,...,x_n^2$ ,  $y_1^2,...,y_p^2$ ) as a disjoint sum of products (DSoP)  $D_i$  that is as a sum in which products are orthogonal each other. All paths connecting this root with 0-terminal node represent an inversion of this function as DSoP  $\overline{D}_i$  in the same way.

Two products are orthogonal if some variable appears in one product without inversion and in another – with inversion.

Fig. 2. 2-length combinational equivalent

#### 1.1. 01 transition probability

Extract a product K from the  $D_i$  that either contains literal  $\overline{y}_i^2$  or variable  $y_i^2$  is absent in K. In the last case we add literal  $\overline{y}_i^2$  to product K. This product encloses in general case both the input and the state variables.

Notice that the state variables correspond to the transition functions  $\psi_1^1,...,\psi_p^1$  that depend on the input variables  $x_1^1,...,x_n^1$  and the state variables  $y_1^1,...,y_p^1$  and all these variables are statistically independent on the input variables  $x_1^2,...,x_n^2$  [2]. It means that we may substitute instead of the variables  $x_1^2,...,x_n^2$  of the product K their probabilities and do that with each product from the  $D_i$ , selected above mentioned way. We have got the following sum:  $\sum b_j k_j$

Here  $b_j$  is result of multiplications of the probabilities  $\rho(x_1),...,\rho(x_n)$  of the proper input variables from a set  $\{x_1^2,...,x_n^2\}$  and  $k_j$  consists of some state variables (possibly with inversions) from a set  $\{y_1^2,...,y_p^2\}$ . The different functions corresponding to the state variables of the product  $k_j$  (they are represented with the  $C^1$  copy) in general case depend on the same variables and these functions are statistically dependent.

Represent corresponding to the product  $k_j$  conjunction of the state variable functions with the BDD-graph.

We may calculate a probability of this conjunction using the given probability distribution for the input and the state variables.

Multiply the result by  $b_j$ . Execute this with each product K from the  $D_i$ . Summing results we calculate the 01 transition probabilities.

# 1.2. Example of calculating 01 transition probability

Consider an example to illustrate the above mentioned results. The transition functions of a copy of the combination equivalent are represented with the following shared

$y_1$   $x_1$   $y_2$   $y_2$   $y_2$   $y_2$   $y_2$

Fig. 3. Shared BDD

BDD (Fig. 3). For simplicity we don't use upper indexes of variables.

Let probabilities of the 1 value of the internal and the state variables be the same and equal to 1/2:  $\rho(x_1) = \rho(x_2) = \rho(y_1) = \rho(y_2) = 1/2$ .

Select the state variable  $y_i^{2'}$  (Fig. 2). Extract the corresponding DSoP from the shared BDD (Fig. 3). Here we take into consideration upper indexes:  $y_1^{2'} = x_1^2 x_2^2 \vee \overline{x}_1^2 y_2^2$ .

All products do not contain  $y_1^2$ . Consequently we need add the literal  $\overline{y}_1^2$  to each product. As a result we have got DSoP  $D^*$ :  $x_1^2 x_2^2 \overline{y}_1^2 \vee \overline{x}_1^2 \overline{y}_1^2 y_2^2$ .

Substitute probabilities instead of the variables  $x_1^2$ ,  $x_2^2$  and obtain the following result:  $1/4 \overline{y_1^2} \vee 1/2 \overline{y_1^2} y_2^2$ .

Extract the functions  $\overline{\psi}_1^1, \psi_2^1$ , corresponding to the  $\overline{y}_1^2$ ,  $y_2^2$  from the shared BDD (Fig. 2 and 3):

$$\overline{y}_{1}^{2} = \overline{x}_{1}^{1} \overline{y}_{2}^{1} \vee x_{1}^{1} \overline{x}_{2}^{1};$$

$$\rho(\overline{y}_{1}^{2}) = 1/4 + 1/4 = 1/2;$$

$$y_{2}^{2} = \overline{x}_{1}^{1} \vee x_{1}^{1} y_{1}^{1} y_{2}^{1}.$$

The conjunction of these functions is represented with the expression:  $(\overline{x}_1^1 \overline{y}_2^1 \vee x_1^1 \overline{x}_2^1) \wedge (\overline{x}_1^1 \vee x_1^1 y_1^1 y_2^1)$ .

The BDD of this expression is represented on Fig. 4. Extract DSoP, representing the conjunction  $\overline{y}_1^2 y_2^2$ :  $\overline{x}_1^1 \overline{y}_2^1 \vee x_1^1 \overline{x}_2^1 y_1^1 y_2^1 = 1/4 + 1/16 = 5/16$ .

Fig. 4. BDD representation of the conjunction  $\overline{y}_1^2 y_2^2$

We could calculate  $\rho(\overline{y}_1^2 y_2^2)$  directly from the BDD of Fig. 4.

Substitute into the expression marked with (\*) the obtained probabilities and calculate the probability of 01 transition:  $\rho$  (01) = 1/4\*1/2 + 1/2\*5/16 = 9/32.

## 1.3. 10 transition probability

To calculate 10 transition probabilities we need obtain DSoP of  $\overline{D}_i$  from shared BDD selecting root that correlates with the variable  $y_i^{2'}$ . Then we choose the products from  $\overline{D}_i$  with the literal  $y_i$  and the products that does not contain the variable  $y_i$  adding to the last products the literal  $y_i$ . For each chosen product we execute the steps of the point A.

### 2. A probability calculation of manifestation of robust PDFs for state variable

Consider the problem of probability calculation of manifestation of robust PDFs for state variable. First we consider robust PDF test pair properties [3]. For that we will examine the equivalent normal form (ENF) of a combinational equivalent copy.

## 2.1. Robust PDF test pair properties

An equivalent normal form represents the function implementing with the circuit and all the circuit paths. Each ENF literal is supplied with the index sequence enumerating the gates of the path. It should be noted that a literal with the same index sequence may appear in different ENF products. The ENF of the circuit (Fig. 5) is as follows (1).

Fig. 5. The combinational circuit  $\overline{a}_{1459} \, b_{59} \, e_{59} \, \lor \, b_{59} \, \overline{c}_{23459} \, d_{3459} e_{59} \lor \lor \, d_{14689} \, \overline{b}_{789} \, c_{234689} \lor \, a_{14689} \, \overline{c}_{234689} \, \overline{d}_{789} \lor \, a_{14689} \, \overline{b}_{789} \, \overline{d}_{34689} \lor \, a_{14689} \, \overline{d}_{34689} \, \overline{d}_{789}$

If literals have the same index sequences but their variables are opposite in sign then we call them as opposite literals. The same variables  $x_i, \overline{x_i}$  being opposite in sign we call opposite variables. Opposite literals are absent in an ENF but opposite variables may present. We will spread all operations on products of a SoP (Sum of Products) on ENF products. We call an ENF product empty if it contains opposite variables. Notice that an ENF empty product consists of different literals.

Examine non-empty products of ENF. Any such product turns into SoP product after elimination of index sequences from literals followed with elimination of repeated variables. Sum of obtained products is SoP representing the function f. Non empty ENF product call implicant of the function f.

We consider single robust PDF of the path  $\alpha$  in the circuit for the appropriate transitions along the path [3] as the temporary  $a_p(b_p)$ -fault of the ENF literal  $x_{i\alpha}$ . This fault

lasts during time  $\omega$ ,  $\omega > \tau$ . Here  $\tau$  is the time passing between adjacent synchronizing signals of the circuit.

The literal  $x_{i\alpha}$  is changed for the constant 1 ( $b_p$ -fault) in ENF products when the corresponding PDF activates the 1 value instead of the expected 0 value on the relevant circuit output and a vector  $v_2$ . This PDF corresponds to falling transition.

The literal  $x_{i\alpha}$  is changed for the constant 0 ( $a_p$ -fault) in ENF products when the corresponding PDF activates the 0 value instead of the expected 1 value on the relevant circuit output and a vector  $v_2$ . This PDF corresponds to rising transition.

A test pattern  $v_2$  in the PDF test pair  $v_1$ ,  $v_2$  is a test pattern for  $b_p(a_p)$ -fault of ENF.

Let K be ENF product (in partly K may be empty ENF product). K is expansible with the literal  $x_{i\alpha}$  if elimination of this literal gives rises to product  $K^*$  that is implicant of the function f. Otherwise K is not expansible with the  $x_{i\alpha}$ .

Elimination of the literal from a product modifies the given ENF (K changes for K\*). If K\* is non-empty product and K\* is non implicant of the function f, then f changes along with ENF. It means that the 1 value area of the function f increases.

$K^*$  is the result of glue of products K and  $\overline{K}$ . Here  $\overline{K}$  is obtained from K with changing the literal  $x_{i\alpha}$  for opposite literal. We will call  $\overline{K}$  as addition of K.

We suppose that the variable  $x_i$  in the literal  $x_{i\alpha}$  doesn't have an inversion. First consider  $b_p$ -fault of the literal  $x_{i\alpha}$ .

Let **K** be a set of ENF products so that each product does not contain  $x_{i\alpha}$ .

Divide the rest ENF products into two sets: one of them  $K_{rxi}$  consists of products so that each of them has repeating variable  $x_i$  (the same variables with the same sign of inversion and the different index sequences). Products of  $K_{rxi}$  don't change the function f when  $b_p$ -fault takes place and consequently not generate test pattern  $v_b$  for  $b_p$ -fault.

Another set  $K_{sxi}$  consists of the products (empty and non-empty) without repeating variable  $x_i$ .

Let K be non-empty product from  $K_{sxi}$ . If K is non-expansible product by literal  $x_{i\alpha}$  then changing that literal for the constant 1 in K alters the function f. That may be detected with a test pattern  $v_b$  which turns into 1 the product  $\overline{K}$  and turns into 0 fault free ENF. This test pattern is at the same time test pattern  $v_2$  from a test pair  $v_1$ ,  $v_2$  for the corresponding PDF. Notice that  $v_b$  turns into one the product  $K^*$  possibly together with other products derived from  $K_{svi}$  by changing the literal  $x_{i\alpha}$  for the constant 1.

If K is expansible product by literal  $x_{i\alpha}$  then changing that literal for the constant 1 does not alter the function f. It means that there is no test pattern  $v_b$  for  $b_p$ -fault originated by the product K.

#### b<sub>v</sub>-fault

Consider  $b_p$ -fault of the literal  $x_{i\alpha}$  and test pattern  $v_b$  that satisfies above mentioned conditions. Variable  $\overline{x}_i$  take the 1 value on  $v_2$ .

Denote as u the minimal cube covering  $v_1$ ,  $v_2$  and as k(u) – the product representing u.

**Theorem 1.** To derive robust PDF test pair  $v_1$ ,  $v_2$  corresponding to  $b_p$ -fault we need the following.

- 1.  $v_2$  is a test pattern for  $b_p$ -fault;

- 2. Variable  $x_i$  in  $v_1$ ,  $v_2$  takes the opposite values;

- 3. k(u) is orthogonal to each product from K;

- 4. Test pattern  $v_1$  turns into 1 product K from  $K_{svi}$  that generates test pattern  $v_b$ .

**Corollary 1.** The function f takes the 0 value on  $v_2$  and takes the 1 value on  $v_1$ .

Corollary 2. Empty product K from  $K_{svi}$  doesn't originate robust PDF test pair.

**Corollary 3.**  $v_1$  is a test pattern for  $a_p$ -fault.

As k(u) is orthogonal to all products of K then  $v_1$  is orthogonal to all products of K but  $v_1$  turns into 1the function f. It means that  $v_1$  is a test pattern for  $a_p$ -fault.

### a<sub>p</sub>-fault

Now consider  $a_p$ -fault of the literal  $x_{ia}$ . All products from K remain in the fault ENF.

The rest products of the fault free ENF are divided into two sets: one of them  $K_{exi}$  consists of the empty products and another  $K_{nexi}$  consists of the non-empty products. The products of  $K_{exi}$  do not change the function f when  $a_p$ -fault takes place and consequently not generate test pattern  $v_a$ .

Consider the set  $K_{nexi}$ . All its products disappear when  $a_p$ -fault takes place. If it changes the function f then there exists a test pattern  $v_a$  that detects  $a_p$ -fault. The test pattern turns into 1 some products from  $K_{nexi}$  and turns into 0 the rest products of the fault free ENF. The test pattern  $v_a$  also turns into 1 the variable  $x_i$ .

**Theorem 2.** To derive robust PDF test pair  $v_1$ ,  $v_2$  corresponding to  $a_p$ -fault we need the following.

- 1.  $v_2$  is a test pattern for  $a_p$ -fault;

- 2. Variable  $x_i$  in  $v_1$ ,  $v_2$  takes the opposite values;

- 3. k(u) is orthogonal to each product from K;

- 4. There exists product K from  $K_{nexi}$  that does not contain repeated variable  $x_i$  so that values of the variables of the cube representing this product and values of the variables of test patterns  $v_1$ ,  $v_2$  (except variable  $x_i$ ) coincide.

**Corollary 1.** The function f takes the 1 value on  $v_2$  and takes the 0 value on  $v_1$ .

**Corollary 2.**  $v_1$  is a test pattern for  $b_p$ -fault.

As k(u) is orthogonal to all products of K then  $v_1$  is orthogonal to all products of K and by the construction  $v_1$  turns into 1 the addition of the product K. It means that  $v_1$  is a test pattern for  $b_p$ -fault.

# 2.2. A probability calculation of robust PDF manifestation for the given path

Represent as the DSoP all robust test pairs for the given path originated by one product of ENF. For that we have to find product K from  $K_{nexi}$  that does not contain repeated variable  $x_i$  and obtain the SoP D from the set K fixing the variables of the product K except  $x_i$ . All roots of the equation D = 0 are represented either as ROBDD or

Free BDD. Each path from the root till the 1-terminal node arises to the product, corresponding to  $2^{n-1-r}$  robust test pairs consisting of neighboring Boolean vectors. Here r is a rank of the product and n is the number of ENF variables. (Notice that the variable  $x_i$  is absent in the product). Having got the BDD for each K from  $K_{nexi}$  that does not contain repeated variable  $x_i$  and corresponds to the same path  $\alpha$  we may execute disjunction operation on these BDDs and ob-

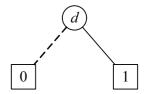

Fig. 6. BDD representation of the product *d*

tain BDD representing all robust test pairs. Using the last BDD we may calculate a probability of the robust PDF manifestation for the path  $\alpha$  substituting instead of the variables their probabilities from the probability distribution.

Illustrate that procedure by an example. Let the variable c be a state variable. First consider the literal  $c_{234689}$ . Take into consideration that for the product  $a\overline{b}c$ ,  $k(u)=a\overline{b}$ , and the corresponding D,  $D=\overline{d}\vee\overline{d}$   $\overline{d}$ . The BDD represents the only product d.

Consider forth product of the ENF that contains the literal  $c_{234689}$ . In this case  $K = ac \, \overline{d}$ ,  $k(u) = a \, \overline{d}$ ,  $D = \overline{b} \vee 1 = 1$ . The equation D = 0 has no roots.

Consequently a probability of robust test pair manifestation for the path  $\alpha$  corresponding to the literal  $c_{234689}$  is represented by the formula  $a\overline{b}d$  and is equal to 1/2\*1/2\*1/2=1/8.

Here we suppose 1 value probability of each variable is equal to 1/2.

When we consider a state variable we have to regard all paths (literals) connected with this variable. Derive for each path a probability of robust PDF manifestation in the above mentioned way. Then we have to summarize these probabilities.

Notice that a test pair for one path does not change the signal values of other path corresponding to the same variable as all products representing another paths are contained in a set *K* formed for the path considered. It means that sensitizations of different paths of the same variable are statistically non-compatible events.

Let c be state variable. We additionally have to find a probability of robust PDF manifestation for the path corresponding to the literal  $\overline{c}_{23459}$ . Then  $K = b \, \overline{c} \, de$ , k(u) = b de,  $D = \overline{a}$ .

BDD originates the only root: product a. Consequently a probability of robust PDFs manifestation for the path corresponding to the literal  $\overline{c}_{23459}$  is represented by the formula *abde*. It is equal to 1/2\*1/2\*1/2\*1/2=1/16. Then a probability of manifestation of robust PDFs for the state variable c is as follows: 1/8+1/16=3/16.

We have got the following experimental results.

Controllability *Pc* and observability *Po* have been calculated for each state variable for some benchmarks. Flip-flops corresponding to state variables with low controllability or/and observability can be selected for including in enhanced scan chains. The additional investigations are necessary for choosing the threshold values for probability and observability We may only say that flip-flops with zero observability must not be included in enhanced scan chains.

The algorithm of estimation calculation of flip-flop observability is based on ENF analysis and using BDDs. ENF is very complicate formula for real circuits. It is possible to use OR/AND tree to present all paths of a circuit [6]. These trees are used for finding the estimations for benchmarks of the Table 1.

We may use for description of the ENF of a circuit the system OR-AND trees. The complexity of the system is linear function of the number of the circuit gates [6]. To accelerate the calculation of flip-flop observability it is possible to joint application of the system OR-AND trees and the corresponding system SSBDDs [7]. We hope that these techniques will allow calculating flip-flop observability for more complicate circuits.

## **Experimental results on Iscas89 benchmarks**

| Circuit | Flip-flops | State Variable | Pc    | Po    |

|---------|------------|----------------|-------|-------|

| s27     | 3          | G11            | 0.172 | 0.125 |

|         |            | G10            | 0.457 | 0.063 |

|         |            | G13            | 0.344 | 0.250 |

| s344    | 15         | ACVG3VD1       | 0.331 | 0.219 |

|         |            | ACVG2VD1       | 0.260 | 0.219 |

|         |            | AM3            | 0.125 | 0.875 |

|         |            | ACVG4VD1       | 0.180 | 0.219 |

|         |            | CNTVG2VD       | 0.188 | 0.375 |

|         |            | AM2            | 0.281 | 0.875 |

|         |            | CNTVG3VD       | 0.188 | 0.500 |

|         |            | AM1            | 0.281 | 0.875 |

|         |            | AM0            | 0.281 | 0.875 |

|         |            | MRVG3VD        | 0.500 | 0.125 |

|         |            | MRVG4VD        | 0.641 | 0.125 |

|         |            | MRVG1VD        | 0.406 | 0.125 |

|         |            | MRVG2VD        | 0.406 | 0.125 |

|         |            | CNTVG1VD       | 0.594 | 0.375 |

|         |            | ACVG1VD1       | 0.280 | 0.219 |

| s444    | 21         | G58            | 0.209 | 0.141 |

|         |            | G112           | 0.335 | 0.000 |

|         |            | G49            | 0.063 | 0.063 |

|         |            | G111           | 0.224 | 0.000 |

|         |            | G45            | 0.094 | 0.188 |

|         |            | G41            | 0.125 | 0.125 |

|         |            | G113           | 0.130 | 0.000 |

|         |            | G162BF         | 0.129 | 0.453 |

|         |            | G80            | 0.133 | 0.343 |

|         |            | G70            | 0.091 | 0.186 |

|         |            | G101           | 0.375 | 0.500 |

|         |            | G66            | 0.113 | 0.275 |

|         |            | G110           | 0.233 | 0.000 |

|         |            | G62            | 0.119 | 0.230 |

|         |            | G109           | 0.099 | 0.000 |

|         |            | G84            | 0.120 | 0.382 |

|         |            | G92            | 0.108 | 0.362 |

|         |            | G155           | 0.375 | 0.500 |

|         |            | G88            | 0.115 | 0.402 |

|         |            | G114           | 0.026 | 0.000 |

|         |            | G37            | 0.578 | 0.000 |

## Conclusion

The special estimations of flip-flop controllability and observability are developed. They may be used for including flip-flops into partial enhanced scan chains. Possibilities of their application to more complicate circuits are noted.

#### REFERENCES

- Xu G., Singh A. D. Achieving high transition delay fault coverage with partial DTSFF enhanced scan chains // Proceedings of International Test Conference. 2007. P. 1–9.

- Xu G., Singh A. D. Flip-flop selection to maximize TDF coverage with partial enhanced scan // Proc. ATS2007. 2007. P. 335–340.

- 3. Wang S. Low overhead partial enhanced scan technique for compact and high fault coverage transition delay test patterns / S. Wang, W. Wei // Proc. ETS2008. 2008. P. 125 –130.

- Matrosova A. Random simulation of logical circuits //Automation and Remote Control. 1995.

No. 1. P. 156–164.

- Matrosova A., Lipsky V., Melnikov A., Singh V. Path delay faults and ENF // Proc. EWDT Symposium, Russia, St. Petersburg, September, 2010. P. 164–167.

- 6. *Matrosova A., Andreeva A., Melnikov A., Nikolaeva E.* Multiple stuck-at fault and path delay fault testable circuits // Proc. EWDT Symposium. 2008. P. 356–364.

- Ubar R. Multi-valued simulation of digital circuits with structurally synthesized binary decision diagrams // OPA (Overseas Publishers Assotiation) N.V. Gordon and Breach Publishers, Multiple Valued Logic. 2001. V. 4. P. 141–157.

Matrosova Anzhela Yu., Melnikov Alexey V.,

Mukhamedov Ruslan V., Ostanin Sergey A.

Tomsk State University

Singh Virendra. Indian Institute of Technology Bombay

E-mail: maull@yandex.ru; alexey.ernest@gmail.com; predictor@yandex.ru;

ostanin@mail.tsu.ru; virendra@computer.org

Поступила в редакцию 12 января 2012 г.

Матросова А.Ю., Мельников А.В., Мухамедов Р.В., Останин С.А. (Томский государственный университет), Сингх В. (Индийский институт технологий, Бомбей). Выбор триггеров в частичные цепи для методов сканирования схем с памятью.

Ключевые слова: неисправность задержки пути, робастно тестируемый путь, эквивалентная нормальная форма (ЭН $\Phi$ ).

При тестировании неисправностей задержек путей схем с памятью используется метод сканирования путей. Существующие архитектурные решения, обеспечивающие реализацию метода сканирования, не позволяют подавать на тестируемую схему любую пару тестовых наборов. Одним из выходов в этой ситуации является использование частичных цепей сканирования с дублирующими триггерами. В эти цепи включаются лишь некоторые триггеры схемы с памятью. В данной работе предлагается включать в частичные цепи сканирования триггеры с низкими оценками управляемости и наблюдаемости. Разработан алгоритм вычисления управляемости переменной состояния, основанный на анализе комбинационного эквивалента длины два. Предложен алгоритм вычисления наблюдаемости переменной состояния, основанный на анализе эквивалентной нормальной формы (ЭНФ). Проведены испытания обоих алгоритмов на контрольных примерах ISCAS'86.