# ВЕСТНИК ТОМСКОГО ГОСУДАРСТВЕННОГО УНИВЕРСИТЕТА

2025 Управление, вычислительная техника и информатика Tomsk State University Journal of Control and Computer Science

№ 72

Научная статья УДК 519.7

doi: 10.17223/19988605/72/13

# О возможностях замены произвольных тестовых пар, обнаруживающих робастно тестируемые неисправности задержек пути, на тестовые пары, соседние по входной переменной пути

# Анжела Юрьевна Матросова<sup>1</sup>, Вячеслав Зиновьевич Тычинский<sup>2</sup>

$^{1,\,2}$  Национальный исследовательский Томский государственный университет, Томск, Россия  $^{1}$  mau11@ yandex.ru  $^{2}$  tvz.041@ yandex.ru

Аннотация. Обнаружение робастно тестируемых неисправностей задержек путей является важным этапом тестирования интегральных схем высокой производительности. Ранее было показано, что использование тестовых пар булевых векторов, соседних по входной переменной пути, позволяет существенно сокращать потребление мощности при тестировании таких неисправностей. Тестовые пары строятся на основе использования булевой разности пути. В данной работе выясняются возможности замены произвольных тестовых пар, обнаруживающих робастно тестируемые неисправности задержек пути, тестовыми парами, состоящим из булевых векторов, соседних по входной переменной пути. Такая замена ориентирована на снижение потребляемой мощности при тестировании по сравнению с последовательностями, построенными из тестовых пар, состоящих из векторов с произвольным расстоянием по Хеммингу.

**Ключевые слова:** комбинационные схемы; эквивалентная нормальная форма (ЭНФ); робастно тестируемые неисправности задержек пути; булева разность пути.

**Для цитирования:** Матросова А.Ю., Тычинский В.З. О возможностях замены произвольных тестовых пар, обнаруживающих робастно тестируемые неисправности задержек пути, на тестовые пары, соседние по входной переменной пути // Вестник Томского государственного университета. Управление, вычислительная техника и информатика. 2025. № 72. С. 134–143. doi: 10.17223/19988605/72/13

Original article

doi: 10.17223/19988605/72/13

# About changing arbitrary test pairs detecting robust testable PDFs for ones consisting of neighbor Boolean vectors

Anzhela Yu. Matrosova<sup>1</sup>, Vyacheslav Z. Tychinskiy<sup>2</sup>

<sup>1, 2</sup> National Research Tomsk State University, Tomsk, Russian Federation

<sup>1</sup> mau11@yandex.ru

<sup>2</sup> tvz.041@yandex.ru

**Abstract**. Detection of robust testable path delay faults is an important step in testing of high-performance integrated circuits. It has been previously shown that using test pairs of Boolean vectors adjacent in the input path variable allows a significant reduction of power consumption when testing such faults. These test pairs are derived from path Boolean difference/ In this paper, we investigate a possibility of replacing of arbitrary test pairs that detect robust testable path delay faults with test pairs consisting of Boolean vectors adjacent in the input path variable. Such replacement can be useful when forming test sequences from arbitrary test pairs aimed at reducing power consumption.

**Keywords:** combinational circuits; Equivalent Normal Forms (ENFs); robust testable Path Delay Faults (PDFs); path Boolean difference.

For citation: Matrosova, A.Yu., Tychinskiy, V.Z. (2025) About changing arbitrary test pairs detecting robust testable PDFs for ones consisting of neighbor Boolean vectors. Vestnik Tomskogo gosudarstvennogo universiteta. Upravlenie, vychislitelnaja tehnika i informatika – Tomsk State University Journal of Control and Computer Science. 72. pp. 134–143. doi: 10.17223/19988605/72/13

#### Введение

Известно, что в логических схемах высокой производительности, характеризующихся высокими скоростями функционирования и наноразмерами транзисторов, возникают непредусмотренные сопротивления, емкости, индуктивности, которые не удается рассчитать заранее. Они приводят к замедлению работы схемы по сравнению с расчетными значениями, что весьма нежелательно.

Одной из наиболее распространенных математических моделей, используемых для выявления задержек в процессе функционирования логических схем, является модель неисправности задержек пути (Path Delay Fault (PDF) модель) [1]. В рамках этой модели предполагается, что задержки отдельных элементов пути и отдельных линий связей между элементами пути достаточно малы и не влияют на расчетную скорость функционирования схемы. В то же время задержка пути в целом может превышать время между синхросигналами и искажать поведение схемы. Такие задержки необходимо обнаруживать и, если возможно, устранять или маскировать.

Обычно тестовые последовательности для выбранного подмножества путей строятся с использованием одной тестовой пары для каждого из путей и выбранного типа перепадов сигналов вдоль рассматриваемого пути [1, 2]. Расстояние по Хеммингу между наборами пары может быть произвольным. (Договоримся в дальнейшем двоичные наборы и булевы векторы считать синонимами.)

Известно, что тестирование задержек в схемах высокой производительности связано со значительным потреблением мощности и может привести к разрушению схемы, несмотря на возможность корректно работать в предписанном ей режиме функционирования. В связи со сказанным необходимо тестировать схемы, ориентируясь на сокращение потребляемой при тестировании мощности [3–8]. В данной работе выясняются возможности замены произвольных тестовых пар, обнаруживающих робастно тестируемые неисправности задержек пути, тестовыми парами, состоящими из булевых векторов, соседних по входной переменной пути. Такая замена ориентирована на снижение потребляемой мощности при тестировании по сравнению с последовательностями, построенными из тестовых пар, состоящих из векторов с произвольным расстоянием по Хеммингу.

**Основные определения.** Введем ряд необходимых понятий, связанных с тестированием неисправностей задержек путей в комбинационной схеме (комбинационной составляющей последовательностной схемы).

Путем схемы называют последовательность элементов схемы, в которой выход предыдущего элемента является входом последующего, причем один из входов первого элемента пути является входом схемы, а выход последнего элемента пути является выходом схемы.

Задержки пути обнаруживаются тестовыми парами  $(v_1, v_2)$  из двух булевых векторов следующим образом. Пусть в момент времени  $t_1$  на вход комбинационной схемы подается входной вектор  $v_1$ . При поступлении следующего синхроимпульса в момент времени  $t_2$  на вход схемы подается вектор  $v_2$  тестовой пары. В момент  $t_3$  с приходом очередного синхроимпульса наблюдается значение переменной на выходе, сопоставляемом этому пути. Если наблюдаемое значение не совпадает с ожидаемым значением, делается вывод, что в схеме имеют место непредусмотренные задержки сигналов. Задержки могут проявляться необязательно на исследуемом пути.

Будем иметь в виду, что задержки противоположных перепадов сигналов вдоль рассматриваемого пути могут различаться, поэтому для каждого типа перепадов в общем случае необходимо отыскивать собственную пару  $(v_1, v_2)$  входных булевых векторов, на которой задержка проявляется.

Перепадам значений сигнала вдоль пути присвоены разные названия. Перепад сигналов, при котором на выходе схемы, сопоставляемом пути, значение сигнала меняется с 1 на 0 в англоязычной литературе принято называть falling transition, а с 0 на 1 – rising transition. В дальнейшем будем использовать эти названия для различения перепадов сигналов пути.

Неисправность задержки пути является робастно тестируемой, если существует тестовая пара, на которой задержка рассматриваемого пути обнаруживается независимо от задержек других путей схемы.

Неисправность задержки пути называют не робастно тестируемой, если она может обнаруживаться тестовой парой только при отсутствии задержек других путей. Это значит, что проявление

неисправности на тестовой паре для не робастно тестируемой неисправности может не означать, что неисправность имеет место именно на пути, для которого тестовая пара построена. Что касается робастно тестируемой неисправности, то ее обнаружение позволяет определить путь, на котором неисправность проявляется. Такую неисправность можно затем маскировать или попытаться перепроектировать с целью исключения задержки и восстановления расчетного быстродействия.

Как известно, тестирование неисправностей задержек путей на практике выполняется методом сканирования, при котором вектор  $v_2$  тестовой пары получается из вектора  $v_1$  либо сдвигом  $v_1$ , либо  $v_2$  порождается реакцией комбинационной схемы на вектор  $v_1$ . Отметим, что векторы  $v_1$ , как правило, являются тестовыми наборами для константных неисправностей комбинационной схемы (комбинационной составляющей схемы с памятью). При таком подходе тестовые пары для робастно тестируемых неисправностей далеко не всегда удается сформировать. Поэтому наряду с традиционным методом сканирования развиваются альтернативные методы тестирования неисправностей задержек пути, в рамках которых тестовые пары вычисляются точно. Это Random Access Scan (RAS) метод, который позволяет существенно сократить время тестирования, потребление мощности и множество тестовых наборов [9, 10]. При реализации этого метода может использоваться как традиционный подход к получению тестовых пар на основе анализа структуры логической схемы с использованием многозначных алфавитов [2], так и на основе вычисления булевой разности пути [11, 12]. При традиционном подходе поиска тестовых пар [9, 10] в общем случае получаются пары с расстоянием по Хеммингу между булевыми векторами пары, большим единицы. Договоримся в дальнейшем слова «наборы» и «векторы» считать синонимами.

В работе проводится исследование возможностей замены тестовой пары с произвольным расстоянием по Хеммингу между векторами, ее составляющими, на векторы, соседние по входной переменной пути. Такая замена ориентирована на снижение потребляемой мощности при тестировании. С этой целью рассматриваются свойства произвольных тестовых пар, обнаруживающих робастно тестируемые неисправности задержек путей, сформулированные в работе [1] с использованием ЭНФ-схемы, а также свойства булевой разности пути, из которой извлекаются тестовые пары соседних булевых векторов.

## 1. Свойства тестовых наборов для обнаружения неисправностей литер ЭНФ

В работе [13] показано, что каждый булев вектор, обращающий булеву разность рассматриваемого пути в единицу, является либо a-тестовым, либо b-тестовым набором для этого пути и соответствующей ему литеры ЭНФ. А именно, если входной набор схемы обращает булеву разность рассматриваемого пути в 1, а схему в 0, то это b-тестовый набор, обнаруживающий  $b_p$ -неисправность литеры ЭНФ. В присутствии  $b_p$ -неисправности схема принимает единичное значение на b-тестовом наборе. Если входной набор обращает схему в 1 и булеву разность рассматриваемого пути в 1, то это a-тестовый набор, обнаруживающий  $a_p$ -неисправность литеры ЭНФ. В присутствии  $a_p$ -неисправности схема принимает нулевое значение на a-тестовом наборе. Будем иметь в виду, что  $b_p$ -неисправность заключается в замене всех литер ЭНФ, сопоставляемых рассматриваемому пути, константой 1,  $a_p$ -неисправность заключается в замене всех литер ЭНФ, сопоставляемых рассматриваемому пути, константой 0. Такие замены мы имеем возможность выполнить, имея ЭНФ схемы.

Обозначим выбранный путь символом  $\alpha$  в комбинационной схеме C, а соответствующую ему литеру  $x_{i\alpha}$ .

Отметим, что изменение значения переменной  $x_i$  в b- и a-тестовом наборах приводит к обращению ЭНФ схемы в 0 и 1 только за счет изменения значения литеры  $x_{i\alpha}$ . Это необходимо учитывать при построении тестовых наборов по ЭНФ, а именно: b(a)-тестовый набор порождается конъюнкциями ЭНФ, не содержащими более одной литеры, помеченной входной переменной пути  $\alpha$ .

Для понимания возможности построения тестовых пар с использованием булевой разности  $D_{\alpha}$  представим процедуру ее построения и отметим свойства  $D_{\alpha}$ .

#### 2. Булева разность пути и ее связь с b, a -тестовыми наборами

Булева разность пути представляется либо в виде ДНФ-, либо ROBDD-графа [11, 12], либо в виде соответствующей схемы (ее единичных наборов [12]). Рассмотрим алгоритм получения булевой разности.

#### 2.1. Получение булевой разности

Представим путь  $\alpha$  для одновыходной комбинационной схемы C, последовательностью следующих символов:  $x_i$ ,  $u_1$ ,  $u_2$ , ...,  $u_{r-1}$ ,  $u_r$ . Здесь  $x_1$ , ...,  $x_n$  – символы входных переменных схемы, r – длина пути  $\alpha$ ,  $x_i$  – переменная, отмечающая начало пути (вход схемы C). Переменные  $u_1$ ,  $u_2$ , ...,  $u_{r-1}$ ,  $u_r$  отмечают выходы элементов пути. Переменная  $u_r$  отмечает выход схемы C. Схема C может быть комбинационной частью последовательностной схемы.

Пусть переменные  $u_i$ ,  $u_{i-1}$ отмечают выходы соседних элементов пути  $\alpha$ . Рассмотрим подсхему  $C_{u_i}$  схемы C. Выход этой подсхемы отмечается переменной  $u_i$ , а входы — переменными  $x_1, \ldots, x_n, u_{i-1}$ . Здесь переменная  $u_{i-1}$  является входной переменной подсхемы  $C_{u_i}$  наряду с переменными  $x_1, \ldots, x_n$  и одновременно входной переменной элемента с выходом, отмеченным переменной  $u_i$ .

Обозначим  $D_{u_i}$  /  $D_{u_{i-1}}$  булеву разность, вычисляемую для функции, реализуемой подсхемой  $C_{u_i}$  по переменной  $u_{i-1}$ . Выражение для булевой разности  $D_{u_i}$  /  $D_{u_{i-1}}$  имеет вид:  $D_{u_i}$  /  $D_{u_{i-1}} = f_{u_i}^{u_{i-1}=0} \oplus f_{u_i}^{u_{i-1}=1}$ , где  $f_{u_i}$  представляет функцию подсхемы  $C_{u_i}$ , зависящую от переменных  $x_1, \ldots, x_n, u_{i-1}$ .

Булева разность для пути α принимает следующий вид:

$$D_{\alpha} = (D_{u_r} / D_{u_{r-1}}) \wedge (D_{u_{r-1}} / D_{u_{r-2}}) \wedge \ldots \wedge (D_{u_2} / D_{u_1}) \wedge (D_{u_1} / D_{x_i}).$$

В работе [7] доказано, что булев вектор  $\gamma$ , обращающий булеву разность  $D_{\alpha}$  в единицу, а схему C в ноль, является b-тестовым набором для  $b_p$ -неисправности ЭНФ. Там же доказано, что булев вектор  $\gamma$ , обращающий булеву разность  $D_{\alpha}$  в единицу и схему C также в единицу, является a-тестовым набором для  $a_p$ -неисправности ЭНФ.

При образовании тестовой пары булев вектор  $\gamma$  является вектором  $v_2$ , а соседний по входной переменной  $x_i$  булев вектор является вектором  $v_1$  для falling и rising transitions. Рассмотрим пример вычисления булевой разности на основе операций над ДНФ

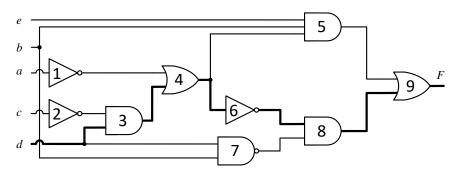

В комбинационной схеме C (рис. 1) выделен путь  $\alpha$ , включающий элементы с номерами 3, 4, 6, 8, 9.

Рис. 1. Комбинационная схема с выделенным путем  $\alpha$  Fig. 1. Combination scheme with a dedicated path  $\alpha$

Начало пути отмечается переменной d. Таким образом,  $\alpha = d$ ,  $u_3$ ,  $u_4$ ,  $u_6$ ,  $u_8$ ,  $u_9$ .

$$D_{u_9} / D_{u_8} = (u_5 \vee (u_8 = 0)) \oplus (u_5 \vee (u_8 = 1)) = \overline{u}_5 = \overline{b} \vee \overline{e} \vee ac \vee a\overline{d} ,$$

$$D_{u_9} / D_{u_6} = ((u_6 = 0) \wedge u_7) \oplus ((u_6 = 1) \wedge u_7) = u_7 = \overline{b} \vee \overline{d} ,$$

$$\begin{split} D_{u_{4}} \ / \ D_{u_{4}} &= (u_{4} = 0) \oplus (u_{4} = 1) = 1 \,, \\ D_{u_{4}} \ / \ D_{u_{3}} &= (u_{1} \vee (u_{3} = 0)) \oplus (u_{1} \vee (u_{3} = 1)) = \overline{u_{1}} = a \,, \\ D_{u_{3}} \ / \ d &= (u_{2} \wedge (d = 0)) \oplus (u_{2} \wedge (d = 1)) = u_{2} = \overline{c} \,\,, \\ D_{\alpha} &= (\overline{b} \vee \overline{e} \vee ac \vee a\overline{d}) \wedge (\overline{b} \vee \overline{d}) \wedge 1 \wedge a \wedge \overline{c} = a\overline{c}\overline{b} \vee a\overline{c}\overline{d} \,\,. \end{split}$$

Итак,  $D_{\alpha}$  представляет все тестовые наборы  $v_2$  для rising и falling transitions, которые не отделены друг от друга. Полезно их разделить.

#### 2.2. Выделение b, а-тестовых наборов и основанных на них триплетов

Если путь  $\alpha$  содержит четное число инверсных вентилей, то для rising transition получаем выражение  $D_{rise} = D_{\alpha} \wedge x_i$ , для falling transition –  $D_{fall} = D_{\alpha} \wedge \overline{x}_i$ . В противном случае  $D_{rise} = D_{\alpha} \wedge \overline{x}_i$  и  $D_{fall} = D_{\alpha} \wedge x_i$ .

Обозначим символами  $D'_{rise}$  и  $D'_{fall}$  выражения, полученные из  $D_{rise}$  и  $D_{fall}$  удалением литеры  $x_i$  (независимо от знака инверсии).

Обозначим символом  $D_{rob}$  выражение, представляющее пары соседних по переменной  $x_i$  наборов:  $D_{rob} = D'_{rise} \wedge D'_{fall}$ . Множество  $D_{rob}$  может быть пустым.

Заметим, что выражение  $D_{rob}$  не содержит переменной  $x_i$ , т.е. булев вектор в пространстве переменных  $x_1, \ldots, x_{i-1}, x_{i+1}, \ldots, x_n$  задает пару в пространстве n переменных. Один из векторов пары получается приписыванием переменной  $x_i$  значения 0, а другой — значения 1. На векторах этой пары достигаются инверсные значения выхода схемы. Оба вектора пары обращают булеву разность в единицу. Один из них является a-тестовым набором, а другой — b-тестовым набором ЭНФ схемы C. Такие пары порождают триплеты тестовых наборов aba и bab, позволяющие обнаруживать робастно тестируемые неисправности задержек пути тремя наборами вместо четырех. Имеется возможность обнаруживать сначала либо rising transition, либо falling transition.

Сравним свойства тестовых пар для робастно тестируемых неисправностей задержек пути: пар с произвольным расстоянием по Хеммингу между тестовыми наборами и пар, состоящих из соседних по входной переменной наборов.

# 3. Свойства тестовых пар для обнаружения робастно тестируемой неисправности задержки пути

#### 3.1. Обнаружение falling transition

Перечисленные ниже свойства тестовых пар представлены в работе [1].

- 1. В случае falling transition, b-тестовый набор (набор  $v_2$  тестовой пары) для  $b_p$ -неисправности обращает выходную переменную схемы, сопоставляемую рассматриваемому пути (ЭНФ исправной схемы), в 0.

- 2. Набор  $v_1$  тестовой пары, отличающийся инверсным значением входной переменной  $x_i$ , а возможно, и значениями других переменных, обращает выходную переменную схемы, сопоставляемую рассматриваемому пути (ЭНФ исправной схемы), в 1.

- 3. Минимально покрывающий интервал векторов тестовой пары для робастно тестируемой неисправности задержки пути должен быть ортогонален конъюнкциям множества  $\mathbf{K}$ . Здесь  $\mathbf{K}$  – конъюнкции ЭН $\Phi$ , не содержащие литеру  $x_{i\alpha}$ .

- 4. При построении b-тестового набора  $v_2$  выполняется условие: с поступлением этого набора происходит смена значения сигналов только одного пути  $\alpha$  (falling transition): иначе тестовая пара не обнаруживает робастно тестируемую неисправность задержки пути  $\alpha$ . Это обеспечивается тем, что порождающие данный набор коньюнкции ЭНФ не содержат более одной литеры, помеченной входной переменной пути  $\alpha$ .

Если минимально покрывающий интервал пары  $(v_1, v_2)$  при выполнении предыдущих условий не ортогонален конъюнкциям множества  $\mathbf{K}$ , то исследуемый путь является не робастно тестируемым, иначе – робастно тестируемым.

Из пары  $(v_1, v_2)$  не соседних булевых векторов, обнаруживающих робастно тестируемую неисправность пути (falling transition), получим пару соседних векторов по входной переменной этого пути, причем одним из векторов новой пары является  $v_2$ .

**Теорема 1.** Тестовая пара, состоящая из булевых векторов с расстоянием по Хеммингу, превосходящим единицу, и обнаруживающая робастно тестируемую неисправность задержки исследуемого пути (falling transition), порождает пару соседних по входной переменной булевых векторов, обнаруживающих эту неисправность.

**Доказательство.** Минимально покрывающий интервал соседних векторов по входной переменной рассматриваемого пути, где  $v_2 - b$ -тестовый набор, в силу своего уменьшения по сравнению с интервалом, порожденным парой не соседних векторов, обнаруживающей робастно тестируемую неисправность, сохраняет ортогональность конъюнкциям множества **К**. В то же время на соседних по входной переменной  $x_i$  векторах пары  $(v_1, v_2)$ , извлеченных из этого интервала, имеем: на наборе  $v_1$  обеспечивается противоположное набору  $v_2$  значение на выходе схемы. Набор  $v_2$  обращает исправную схему в 0, а неисправную схему в 1. За счет того, что  $v_2$  есть b-тестовый набор, обращающий булеву разность в 0, а исходная тестовая пара обнаруживает робастно тестируемую неисправность пути  $\alpha$ , тестовый набор  $v_2$  этой пары (b-тестового набор) обнаруживает неисправность пути  $\alpha$  и только его. Дело в том, что b-тестовый набор порождается конъюнкциями ЭНФ, не содержащими нескольких литер, помеченных входной переменной пути и с тем же знаком инверсии, что  $x_{i\alpha}$ . Теорема доказана.

**Следствие 1.** Пару не соседних по входной переменной булевых наборов, обнаруживающих робастно тестируемую неисправность задержки пути (falling transition), можно заменить парой соседних (по отношению к вектору  $v_2$  исходной пары) по входной переменной  $x_i$  булевых векторов, обнаруживающих эту неисправность при меньшей потребляемой мощности.

# 3.2. Обнаружение rising transition

- 1. Набор  $v_2$  является a-тестовым набором для  $a_p$ -неисправности и обращает выходную переменную схемы, сопоставляемую рассматриваемому пути, в 1.

- 2. Набор  $v_1$ , отличающийся инверсным значением входной переменной  $x_i$ , а возможно, и значениями других переменных, обращает выходную переменную схемы, сопоставляемую рассматриваемому пути, в 0.

- 3. Минимально покрывающий интервал тестовой пары для робастно тестируемой неисправности задержки пути ортогонален конъюнкциям множества  $\mathbf{K}$ .

- 4. Поскольку  $v_2$  является тестовым набором для  $a_p$ -неисправности, то он обращает в единицу хотя бы одну непустую конъюнкцию ЭНФ с литерой  $x_{ia}$ , являясь ортогональным всем конъюнкциям множества **К** [1].

- 5. При построении a-тестового набора  $v_2$  выполняется условие: с поступлением этого набора происходит смена значения сигналов только одного пути  $\alpha$  (rising transition), поскольку иначе тестовая пара не обнаруживает робастно тестируемую неисправность задержки пути  $\alpha$ . Это значит, что в качестве порождающих тестовый набор конъюнкций ЭНФ выбираются те, которые не содержат более одной литеры, помеченной входной переменной пути  $\alpha$  и с тем же знаком инверсии.

Из пары  $(v_1, v_2)$  не соседних булевых векторов, обнаруживающих робастно тестируемую неисправность пути (rising transition), получим пару соседних векторов по входной переменной этого пути, причем одним из векторов новой пары является  $v_2$ .

**Теорема 2.** Тестовая пара, состоящая из булевых векторов с расстоянием по Хеммингу, превосходящим единицу, и обнаруживающая робастно тестируемую неисправность задержки исследуемого пути (rising transition), порождает пару соседних по входной переменной булевых векторов, обнаруживающих эту неисправность.

**Доказательство.** Минимально покрывающий интервал соседних векторов  $(v_1, v_2)$  по входной переменной рассматриваемого пути, где  $v_2 - a$ -тестовый набор, в силу своего уменьшения по сравнению с интервалом, порожденным парой не соседних векторов, обнаруживающей робастно тестируемую неисправность, сохраняет ортогональность конъюнкциям множества **K**. В то же время на соседних по входной переменной  $x_i$  наборах пары  $(v_1, v_2)$ , извлеченных из этого интервала, за счет того, что  $v_2$  есть a-тестовый набор, обращающий булеву разность пути  $\alpha$  в 1, имеем: на наборе  $v_1$  обеспечивается противоположное набору  $v_2$  значение на выходе схемы. Набор  $v_2$  обращает исправную схему в 1, а неисправную схему в 0. Поскольку исходная тестовая пара обнаруживает робастно тестируемую неисправность пути  $\alpha$ , то тестовый набор  $v_2$  этой пары (a-тестового набор) обнаруживает неисправность пути  $\alpha$  и только его. Это обеспечивается тем, что a-тестовый набор порождается конъюнкциями ЭНФ, не содержащими нескольких литер, помеченных входной переменной пути и с тем же знаком инверсии, что  $x_{i\alpha}$ . Теорема доказана.

Следствие 2. Пару не соседних по входной переменной булевых векторов, обнаруживающих робастно тестируемую неисправность задержки пути (rising transition), можно заменить парой соседних (по отношению к вектору  $v_2$  исходной пары) по входной переменной  $x_i$  булевых векторов, обнаруживающих эту неисправность при меньшей потребляемой мощности.

Следствие 3. На основании теорем 1 и 2 пару не соседних по входной переменной булевых векторов, обнаруживающих робастно тестируемую неисправность задержки пути для falling и rising transition, можно заменить двумя парами соседних по входной переменной  $x_i$  векторов: одна пара строится с использованием вектора  $v_2$ , другая — с использованием вектора  $v_1$  исходной пары. Полученные пары обнаруживают неисправности противоположных перепадов значений сигналов пути  $\alpha$  в условиях возможного снижения потребляемой мощности.

Следует иметь в виду, что ЭНФ является чрезвычайно громоздкой формулой. Представление ее в виде размеченного И / ИЛИ дерева хотя и позволяет строить тестовые пары для более сложных комбинационных схем, тем не менее сложность размеченных деревьев экспоненциально возрастает в схемах с большим числом ветвлений. Из сказанного следует, что избавление от использования ЭНФ в любом из ее представлений при поиске тестовых пар очень важно.

Сведение получения тестовых пар для обнаружения неисправностей задержек пути к вычислению булевой разности пути позволяет избавиться от использования ЭНФ. Получаемые при этом тестовые пары характеризуются минимальным потреблением мощности.

# 4. Свойства пар соседних наборов, порождаемых $D_a$ при условии пустого множества $D_{rob}$

Выражение  $D_{rob}$  при любом из перечисленных способов его представления позволяет найти множество всех соседних тестовых пар, обнаруживающих робастно тестируемые задержки противоположных перепадов сигналов для рассматриваемого пути. Однако это множество тестовых пар может оказаться пустым. Выясним, что происходит в этой ситуации с обнаружением неисправностей задержек пути.

В такой ситуации булева разность также представляет в общем случае множество a-тестовых наборов и множество b-тестовых наборов для рассматриваемого пути, однако их соседние по входной переменной наборы не являются соответственно b-тестовыми и a-тестовыми наборами. Отметим, что на соседнем по входной переменной наборе по отношению к набору, обращающему булеву разность в единицу, булева разность в рассматриваемой ситуации принимает значение 0.

**Теорема 3.** Тестовые пары, состоящие из булевых векторов, соседних по входной переменной пути, причем один набор является b-тестовым, а второй не является a-тестовым, не обнаруживают робастно тестируемую неисправность задержки рассматриваемого пути (falling transition).

**Доказательство**. Поскольку второй набор не является a-тестовым, то он либо не ортогонален множеству K, либо для него не существует в ЭНФ порождающей конъюнкции, то есть конъюнкции, которая не содержит более одной литеры, помеченной входной переменной пути  $\alpha$  с тем же знаком инверсии.

В первом случае минимально покрывающий интервал для векторов рассматриваемой пары не ортогонален множеству K. Во втором случае a-тестовый набор невозможно сформировать. Следовательно, такая тестовая пара не обнаруживает робастно тестируемую неисправность задержки этого пути (falling transition). Теорема доказана.

**Теорема 4.** Тестовые пары, состоящие из булевых векторов, соседних по входной переменной пути, причем один набор является a-тестовым, а второй не является b-тестовым, обнаруживают робастно тестируемую неисправность задержки рассматриваемого пути (rising transition).

**Доказательство.** Поскольку второй набор не является b-тестовым, то это значит, что не существует порождающей его конъюнкции ЭНФ, которая бы не содержала более одной литеры, помеченной входной переменной пути  $\alpha$  и с тем же знаком инверсии. На соседнем по входной переменной пути наборе  $v_1$  схема принимает значение 0. Минимально покрывающий интервал для пары ( $v_1$ ,  $v_2$ ) ортогонален множеству **К**. Поскольку в этой ситуации существование a-тестового набора гарантирует изменение входного сигнала только по пути  $\alpha$ , то тестовая пара ( $v_1$ ,  $v_2$ ) обнаруживает робастно тестируемую неисправность рассматриваемого пути (rising transition). Теорема доказана.

#### 5. Обсуждение экспериментальных результатов

С использованием булевой разности пути комбинационной схемы были построены тестовые пары для путей схем из набора бенчмарков ISCAS'89. Для каждого выхода каждой схемы было выбрано не менее 10 самых длинных путей. Общая информация о бенчмарках, использованных при тестировании, представлена в табл. 1.

Информация об использованных бенчмарках

Таблица 1

| $N\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | Бенчмарк | число входов | кодов Число выходов Число вент |     | Выбрано путей |

|-----------------------------------------------------------------------------|----------|--------------|--------------------------------|-----|---------------|

| 1                                                                           | s298     | 17           | 20                             | 119 | 146           |

| 2                                                                           | s344     | 24           | 26                             | 160 | 159           |

| 3                                                                           | s400     | 24           | 27                             | 162 | 258           |

| 4                                                                           | s444     | 24           | 27                             | 181 | 237           |

| 5                                                                           | s641     | 54           | 42                             | 379 | 309           |

| 6                                                                           | s820     | 23           | 24                             | 289 | 232           |

| 7                                                                           | s953     | 45           | 52                             | 395 | 338           |

| 8                                                                           | s1196    | 32           | 32                             | 529 | 334           |

| 9                                                                           | s1488    | 14           | 25                             | 653 | 312           |

| 10                                                                          | s1494    | 14           | 25                             | 647 | 336           |

Таблица 2

| $N_{\underline{0}}$ | Выбрано | Пути без | Пути без         | Путу бар Д                | Ложные пути | Робастно         | Доля робастно     |

|---------------------|---------|----------|------------------|---------------------------|-------------|------------------|-------------------|

| $\Pi/\Pi$           | путей   | а-тестов | <i>b</i> -тестов | Пути оез D <sub>rob</sub> |             | тестируемые пути | тестируемых путей |

| 1                   | 146     | 13       | 7                | 1                         | 24          | 101              | 69,18%            |

| 2                   | 159     | 22       | 16               | 0                         | 2           | 119              | 74,84%            |

| 3                   | 258     | 7        | 9                | 10                        | 4           | 228              | 88,37%            |

| 4                   | 237     | 44       | 23               | 1                         | 21          | 148              | 62,45%            |

| 5                   | 309     | 42       | 68               | 0                         | 56          | 143              | 46,28%            |

| 6                   | 232     | 0        | 0                | 2                         | 0           | 230              | 99,14%            |

| 7                   | 338     | 0        | 0                | 2                         | 0           | 336              | 99,41%            |

| 8                   | 334     | 24       | 22               | 5                         | 119         | 164              | 49,10%            |

| 9                   | 312     | 6        | 3                | 11                        | 1           | 291              | 93,27%            |

| 10                  | 336     | 3        | 4                | 16                        | 0           | 313              | 93,15%            |

В табл. 2 приведена более детальная информация по путям, для которых не существуют тестовые пары такие, что один из векторов является a-тестовым набором, а другой — b-тестовым набором, т.е. множество  $D_{rob}$  пусто:

- пути без a-тестовых наборов, для которых существуют b-тестовые наборы;

- пути без b-тестовых наборов, для которых существуют a-тестовые наборы;

- пути с a- и b-тестовыми наборами, для которых при этом множество единичных наборов  $D_{rob}$  пусто;

- ложные пути, для которых  $D_{\alpha}$  пусто.

#### Заключение

Установлено, что использование булевой разности пути при построении тестовых пар для робастно тестируемых неисправностей задержек пути позволяет обнаруживать те же робастно тестируемые неисправности, которые обнаруживаются методом анализа ЭНФ схемы [1] или методом анализа структуры схемы с использованием многозначных алфавитов [2]. Показано, что тестовая пара не соседних булевых векторов всегда может быть заменена парой или двумя парами соседних по входной переменной пути векторов, порожденных булевой разностью рассматриваемого пути. Этот факт позволяет заменять тестовые последовательности, состоящие из пар не соседних булевых векторов, парами соседних векторов с меньшей потребляемой мощностью и, следовательно, снижать потребляемую мощность тестовой последовательности в целом.

#### Список источников

- 1. Липский В.Б., Матросова А.Ю. Свойства пар тестовых наборов, обнаруживающих неисправности задержек путей в логических схемах VLSI высокой производительности // Автоматика и телемеханика. 2015. № 4. С. 135–148.

- 2. Bushnell M.L. Essentials of Electronic Testing for Digital, Memory, And Mixed-Signal VLSI Circuits. Hingham, MA: Kluwer Academic Publishers, 2000. 432 p.

- 3. Lindgren P., Kerttu M., Thornton M., Drechsler R. Low power optimization technique for BDD mapped circuits // Proc. of the ASP-DAC. 2001. P. 615–621.

- 4. Shelar R.S., Sapatnekar S.S. An efficient algorithm for low power pass transistor logic synthesis // Proc. of the ASP-DAC. 2002. P. 87–92.

- 5. Gekas G., Nikolos D., Kalligeros E., Kavousianos X. Power aware test-data compression for scan-based testing // 2005 12th IEEE International Conference on Electronics, Circuits and Systems, Gammarth, Tunisia. 2005. P. 1–4.

- 6. Tudu J.T., Larsson E., Singh V., Agrawal V.D. On Minimization of Peak Power for Scan Circuit during Test // Test Symposium 2009 14th IEEE European. 2009. P. 25–30.

- Kotasek Z., Skarvada J., Strnadel J. Reduction of Power Dissipation Through Parallel Optimization of Test Vector and Scan Register Sequences // IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems. 2010. P. 364

–369. doi: 10.1109/DDECS.2010.5491750

- 8. Sinduja V., Raghav S., Anita J.P. Efficient don't-care filling method to achieve reduction in test power // 2015 International Conference on Advances in Computing, Communications and Informatics (ICACCI). 2015. P. 478–482.

- 9. Hu Y., Fu X., Fan X., Fujiwara H. Localized Random Access Scan: Towards Low Area and Routing Overhead // Proc. of the 2008 Asia and South Pacific Design Automation Conference. IEEE Computer Society Press, 2008. P. 565–570.

- 10. Adiga R., Arpit G., Singh V., Satuja K.K., Fujivara H., Singh A.D. On Minimization of Test Application Time for RAS // Proc. 23 International Conference on VLSI design. IEEE, 2010. P. 393–398,

- 11. Matrosova A.Yu., Andreeva V.V., Nikolaeva E.A. Finding Test Pairs for PDFs in Logic Circuits Based on Using Operations on ROBDDs // Russian Physics Journal. 2018. V. 61 (5). P. 994–999.

- 12. Matrosova A.Yu , Andreeva V.V., Tychinskiy V.Z., Goshin G.G. Applying ROBDDs for delay testing of logical circuits // Russian Physics Journal. 2019. V. 62 (5). P. 86–94.

- 13. Матросова А.Ю., Тычинский В.З. Андреева В.В. Булева разность и обнаружение неисправностей задержек пути // Вестник Томского государственного университета. Управление, вычислительная техника и информатика. 2024. № 66, С. 108–119. doi: 10.17223/19988605/66/11

#### References

- 1. Lipsky, V.B. & Matrosova, A.Yu. (2015) Properties of pairs of test vectors detecting path delay faults in high performance VLSI logical circuits. *Automation and Remote Control*. 4. pp. 135–148.

- 2. Bushnell, M.L. (2000) Essentials of Electronic Testing for Digital, Memory, And Mixed-Signal VLSI Circuits. Hingham, MA, USA: Kluwer Academic Publishers.

- 3. Lindgren, P., Kerttu, M., Thornton, M. & Drechsler R. (2001) Low power optimization technique for BDD mapped circuits. *Proc. of the ASP-DAC*. pp. 615–621.

- 4. Shelar, R.S. & Sapatnekar, S.S. (2002) An efficient algorithm for low power pass transistor logic synthesis. *Proc. of the ASP-DAC*. pp. 87–92.

- 5. Gekas, G., Nikolos, D., Kalligeros, E. & Kavousianos, X. (2005) Power aware test-data compression for scan-based testing. 2005 12th IEEE International Conference on Electronics, Circuits and Systems. Gammarth, Tunisia. pp. 1–4.

- 6. Tudu, J.T., Larsson, E., Singh, V. & Agrawal, V.D. (2009) On Minimization of Peak Power for Scan Circuit during Test. *Test Symposium 2009. 14th IEEE European.* pp. 25–30.

- Kotasek, Z., Skarvada, J. & Strnadel, J. (2010) Reduction of Power Dissipation Through Parallel Optimization of Test Vector and Scan Register Sequences. *IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems*. pp. 364–369. DOI: 10.1109/DDECS.2010.5491750

- 8. Sinduja, V., Raghav, S. & Anita, J.P. (2015) Efficient don't-care filling method to achieve reduction in test power. 2015 International Conference on Advances in Computing, Communications and Informatics (ICACCI). pp. 478–482.

- 9. Hu, Y., Fu, Fan, X. & Fujiwara, H. (2008) Localized random access scan: towards low area and routing overhead. *Proceedings of the 2008 Asia and South Pacific Design Automation Conference. IEEE Computer Society Press.*, pp. 565–570.

- 10. Adiga, R., Arpit, G., Singh, V., Satuja, K.K., Fujivara H. & Singh A.D. (2010) On minimization of test application time for RAS. *Proceedings 23 International Conference on VLSI design. IEEE.* pp. 393–398.

- 11. Matrosova, A.Yu., Andreeva, V.V. & Nikolaeva, E.A. (2018) Finding Test Pairs for PDFs in Logic Circuits Based on Using Operations on ROBDDs. *Russian Physics Journal*. 61(5). pp. 994–999.

- 12. Matrosova, A.Yu., Andreeva, V.V., Tychinskiy, V.Z. & Goshin, G.G. (2019) Applying ROBDDs for delay testing of logical circuits. *Russian Physics Journal*. 62(5). pp. 86–94.

- 13. Matrosova, A.Yu., Tychinskiy, V.Z. & Andreeva, V.V. (2024) Boolean difference and path delay faults detection. *Vestnik Tomskogo gosudarstvennogo universiteta. Upravlenie, vychislitelnaya tekhnika i informatika Tomsk State University Journal of Control and Computer Science*. 66. pp. 108–119. DOI: 10.17223/19988605/66/11

#### Информация об авторах:

**Матросова Анжела Юрьевна** — профессор, доктор технических наук, профессор кафедры компьютерной безопасности Института прикладной математики и компьютерных наук Национального исследовательского Томского государственного университета (Томск, Россия). E-mail: mau11@yandex.ru

**Тычинский Вячеслав Зиновьевич** – аспирант, ассистент кафедры компьютерной безопасности Института прикладной математики и компьютерных наук Национального исследовательского Томского государственного университета (Томск, Россия). E-mail: tvz.041@yandex.ru

Вклад авторов: все авторы сделали эквивалентный вклад в подготовку публикации. Авторы заявляют об отсутствии конфликта интересов.

#### Information about the authors:

Matrosova Anzhela Yu. (Doctor of Technical Sciences, Professor, Institute of Applied Mathematics and Computer Science, National Research Tomsk State University, Tomsk, Russian Federation). E-mail: mau11@yandex.ru

**Tychinskiy Vyacheslav Z.** (Post-Graduate Student, Assistant, National Research Tomsk State University, Tomsk, Russian Federation). E-mail: tvz.041@yandex.ru

Contribution of the authors: the authors contributed equally to this article. The authors declare no conflicts of interests.

Поступила в редакцию 10.05.2025; принята к публикации 02.09.2025

Received 10.05.2025; accepted for publication 02.09.2025